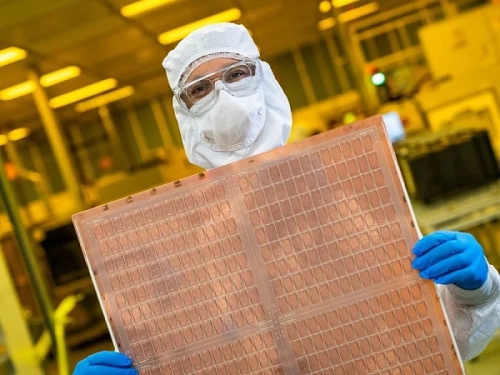

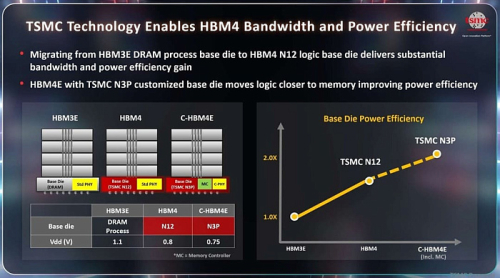

На прошлой неделе TSMC рассказала о своих планах относительно памяти HBM, а точнее её будущих поколений, таких как HBM4 и HBM4E, предлагающих приличные изменения по сравнению с HBM3E, пользующейся спросом со стороны производителей ускорителей для работы с искусственным интеллектом.

Компания отмечает, что стеки HBM4 перейдут на новую логическую матрицу, создаваемую при помощи технологической нормы TSMC N12, за счёт чего получится снизить напряжение с 1.1 до 0.8 В. Более того, переход на HBM4E потребует использования логической матрицы C-HBM4E, которая не только снизит напряжение до 0.75 В и перейдёт на техпроцесс N3P, но и переместит контроллер памяти на базовый слой.

Таким образом, будущая память сможет предложить полутора- и двукратное улучшение энергоэффективности, а также более современные нормы производства. Это будет полезно для ускорителей AMD Instinct MI400 и NVIDIA Vera Rubin, ожидаемых в следующем году.

![⚡️ 40 бесплатных курсов по нейросетям: русские и зарубежные [+видеоуроки]... 1 file_1214.jpg](https://ideipro.ru/wp-content/uploads/2025/12/file_1214.jpg)